リソグラフィ装備市場

リソグラフィ機器の市場規模、シェア、成長、業界分析、タイプ(EUV、DUV)、テクノロジー(ARFスキャナー、KRFステッパー、I-Lineステッパー、ARF浸漬、その他)、アプリケーション(高度なパッケージ、LED、MEMS、電源デバイス)、パッケージングプラットフォーム、地域分析によるアプリケーション( 2024-2031

ページ: 200 | 基準年: 2023 | リリース: 2025年4月 | 著者: Versha V. | 最終更新: 2026年2月

今すぐお問い合わせ

ページ: 200 | 基準年: 2023 | リリース: 2025年4月 | 著者: Versha V. | 最終更新: 2026年2月

市場には、半導体製造に使用される機械と技術が含まれ、シリコンウェーハのマイクロサーキューの正確なパターン化を可能にします。

フォトリソグラフィー、極端な紫外線(EUV)、ディープ紫外線(DUV)、およびナノインプリントリソグラフィシステムが含まれます。このレポートは、主要なドライバーと、予測期間にわたって成長軌道を形作る競争の景観とともに、市場を推進する主要な要因の概要を示しています。

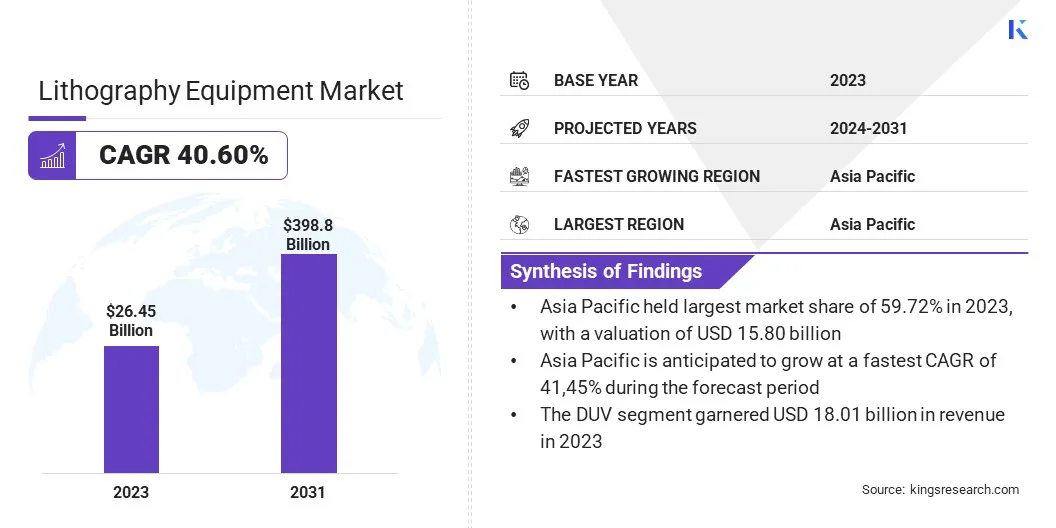

世界のリソグラフィー機器市場の規模は、2023年に264.45億米ドルと評価され、2024年の367億米ドルから2031年までに398.8億米ドルに成長すると予測されており、予測期間中は40.60%のCAGRを示しています。

この市場は、コンシューマーエレクトロニクス、AI、自動車、通信などの業界を介して高度な半導体チップの必要性の増加に駆り立てられているため、急速に拡大しています。

5Gネットワークの展開は、高速で低遅延のチップの必要性を促進しますが、AIと高性能コンピューティングにはより小さく、より強力な半導体が必要であり、の採用が増加します。EUVリソグラフィ。電気自動車(EV)と自律運転技術の人気の高まりにより、高度な半導体成分が必要になり、最先端のリソグラフィープロセスが必要です。

リソグラフィ装備業界で事業を展開している大手企業は、ASML、Nikon Corporation、Canon Inc.、Applied Materials、Inc.、Lam Research Corporation、Suss Microtec SE、EV Group、Jeol Group、Kla Corporation、Veeco Instruments、Raith GmbH、Mycronic、Screen Semiconductor Solutions Co.、Ltd.、Neutronix Quintel、およびNeutronix kintel、およびLtd.

Chiplet Architectureや3D Stackingなどの高度なパッケージング技術へのシフトには、パフォーマンスと効率を改善するために、より正確なリソグラフィソリューションが必要です。

データセンターのエネルギー効率の高い高性能コンピューティングソリューションに焦点を当てているのは、企業が低電力消費により高いトランジスタ密度を可能にするリソグラフィー技術を求めているため、市場の成長にも貢献しています。これらの要因は、次世代のリソグラフィー機器への革新と投資を促進し、持続的な市場拡大を確保します。

マーケットドライバー

High-NA EUVの進歩と半導体需要の増加

市場は、高数値開口(NA)EUVリソグラフィの継続的な進歩と、小型化と電力効率の高い半導体デバイスの需要の増加によって推進されています。

High-NA EUVリソグラフィは主要なブレークスルーであり、シップメーカーがより細かいパターン形成と機能サイズを縮小できるようにすることで、より高い精度とトランジスタ密度を達成できるようにします。これにより、人工知能(AI)や高性能コンピューティングなど、高い計算効率を必要とするアプリケーションに不可欠なチップ性能が向上します。

さらに、業界はよりコンパクトで強力な電子機器を開発しており、半導体デバイスの小型化とエネルギー効率の必要性を推進しています。コンシューマーエレクトロニクス、IoTデバイス、およびAI駆動型アプリケーションには、優れた性能を備えた小さなチップが必要であり、半導体メーカーがサブ2NMプロセスノードに最先端のリソグラフィソリューションを採用するように強制します。

市場の課題

高コストと複雑さ

リソグラフィ装置市場の主要な課題は、高度なリソグラフィー技術、特に高NA EUVシステムに関連する高コストと複雑さです。これらの最先端のツールの開発と展開には、複雑な光学系、精密エンジニアリング、極端な製造条件のため、数十億ドルの投資が必要です。

さらに、これらのシステムを維持および較正するための運用コストは、半導体メーカーの財政的負担を追加します。これにより、小規模なファウンドリと新興プレイヤーが競争することが困難になり、次世代のチップ製造へのアクセスが制限されます。

半導体メーカーと機器のサプライヤーは、金銭的負担を分配するために、コストシェアリングモデル、業界協力、政府が支援するイニシアチブをますます採用しています。企業はまた、プロセス効率の最適化、既存のリソグラフィツールの寿命を拡大し、AI駆動型の自動化を統合して生産性を向上させながらコストを削減することに焦点を当てています。

市場動向

マスクレスリソグラフィとパネルレベルのパッケージ

市場は、マスクレスリソグラフィの出現と、半導体製造におけるパネルレベルのパッケージ(PLP)の採用の拡大とともに進化しています。

マスクレスリソグラフィは、デジタル投影技術または直接洗浄方法を使用することにより、物理的な光腫の必要性を排除し、設計の柔軟性を高めながら、生産時間とマスク関連コストを大幅に削減します。これにより、迅速なプロトタイピングとカスタマイズが可能になり、次世代のチップアーキテクチャに最適です。

同時に、パネルレベルのパッケージは、効率と収量を増加させることにより、半導体製造を最適化しています。円形のウェーハサイズによって制限されている従来のウェーハレベルのパッケージとは異なり、PLPはより大きな長方形の基質を使用して、材料利用率の改善と同時に複数のチップを処理できます。

このアプローチは、廃棄物を削減し、コストを削減し、半導体デバイスの電気性能を高め、AI、IoT、および高速コンピューティングアプリケーションの高性能および費用効率の高いチップの必要性を高めます。

|

セグメンテーション |

詳細 |

|

タイプごとに |

euv、duv |

|

テクノロジーによって |

ARFスキャナー、KRFステッパー、I-Lineステッパー、ARFイマージョン、マスクアライナー、その他 |

|

アプリケーションによって |

高度なパッケージ、LED、MEMS、パワーデバイス |

|

パッケージングプラットフォームによって |

3D IC、2.5Dインターポーザー、ウェーハレベルチップスケールパッケージ(WLCSP)、FO WLPウェーハ、3D WLPなど |

|

地域別 |

北米:米国、カナダ、メキシコ |

|

ヨーロッパ:フランス、英国、スペイン、ドイツ、イタリア、ロシア、ヨーロッパのその他 | |

|

アジア太平洋:中国、日本、インド、オーストラリア、ASEAN、韓国、アジア太平洋地域の残り | |

|

中東とアフリカ:トルコ、アラブ首長国連邦、サウジアラビア、南アフリカ、中東の残りのアフリカ | |

|

南アメリカ:ブラジル、アルゼンチン、南アメリカの残り |

市場セグメンテーション

地域に基づいて、市場は北米、ヨーロッパ、アジア太平洋、中東、アフリカ、ラテンアメリカに分類されています。

アジア太平洋地域は、2023年にリソグラフィ装備市場の36.42%のシェアを占め、158億米ドルの評価を受けました。この地域の市場は、台湾、韓国、中国、日本などの半導体製造ハブの支配によって推進されています。

台湾半導体製造会社(TSMC)と韓国のSamsung Electronicsリードは、高度なノード生産においてリードし、技術的リーダーシップを維持するためにEUVおよびDUVリソグラフィー機器に多額の投資を行っています。製造プロセスにおける継続的な技術的進歩と相まって、主要な半導体ファウンドリーの存在は、地域の成長を促進しました。

さらに、国内の半導体企業への投資の増加と、フォトレジストやマスクブランクなどのフォトリソグラフィー材料における日本の強力な地位は、市場における地域のリーダーシップに貢献しています。

北米のリソグラフィ装備産業は、市場で最速の成長を登録する予定であり、予測期間にわたって40.51%のCAGRが予測されています。この拡張は、高度なチップ生産におけるIntel、GlobalFoundries、Texas Instrumentsなどの大手半導体メーカーからの多額の投資によって推進されています。

この地域は、半導体研究機関と技術の協力の確立された生態系の恩恵を受け、リソグラフィープロセスの継続的な革新を促進します。 AI、量子コンピューティング、および高性能コンピューティングに焦点を当てているため、次世代チップが必要になり、より洗練されたリソグラフィソリューションが必要です。

さらに、Chipletベースの設計や不均一な統合など、高度なチップアーキテクチャの開発に関する北米の強力な専門知識は、高精度リソグラフィ装置の必要性をさらに高めています。

北米は、自立した半導体サプライチェーンと最先端の製造施設の拡大に重点を置いているため、リソグラフィー技術の進歩の重要なハブとして浮上する態勢が整っています。

リソグラフィ機器市場は、市場のリーダーシップを維持するための技術革新、戦略的パートナーシップ、および能力拡大に焦点を当てた主要なプレーヤーによって特徴付けられます。

企業は、解決能力を強化し、スループットを改善し、より小さなノードで費用対効果の高いチップ製造を可能にするために、研究開発に多額の投資を行っています。 EUVリソグラフィーの採用は主要な焦点であり、企業はEUVソースパワーとペリクルテクノロジーの改良に取り組んで効率を向上させています。

主要なリソグラフィー機器メーカーは、半導体ファウンドリーと統合されたデバイスメーカー(IDMS)とともに、次世代の製造技術を共同開発するための提携を結成しています。一部のプレーヤーは、生産施設を拡大し、サプライチェーンを最適化して、高度な半導体製造ツールの世界的なニーズを満たしています。

さらに、企業は、高度なアップグレードキットとモジュール拡張機能を開発することにより、既存のリソグラフィシステムの寿命と効率を拡大することに焦点を当てており、半導体メーカーがまったく新しい機器に投資せずにパフォーマンスを最適化できるようにします。

オーバーレイの精度の向上と、新しい光学的および計算リソグラフィ技術を通じてパターン形成の変動を削減することに重点が置かれ、高度なノード生産におけるより良い収量制御が可能になります。

最近の開発(買収/パートナーシップ/製品の発売)

よくある質問