3Dスタッキング市場

3Dスタッキング市場規模、シェア、成長および業界分析、方法別(チップ対チップ、チップ対ウェーハ、ダイ対ダイ、ダイ対ウェーハ、ウェーハ対ウェーハ)、相互接続技術別(3Dハイブリッドボンディング、3D TSV(スルーシリコンビア)、モノリシック3D統合)、デバイスタイプ別、エンドユーザー産業別、および地域別分析、 2025-2032

ページ: 200 | 基準年: 2024 | リリース: 2025年9月 | 著者: Versha V. | 最終更新: 2026年3月

今すぐお問い合わせ

ページ: 200 | 基準年: 2024 | リリース: 2025年9月 | 著者: Versha V. | 最終更新: 2026年3月

3D スタッキング プロセスでは、複数の半導体層を 1 つのパッケージに統合して、デバイスのパフォーマンスを向上させ、設置面積を削減します。 3D ハイブリッド ボンディング、シリコン貫通ビア、モノリシック 3D 統合などの高度な相互接続技術を組み合わせて、より高い速度、効率、密度を実現します。

このプロセスは、メモリ、ロジック IC、イメージング コンポーネント、LED、MEMS センサーなどのデバイスに適用され、さまざまな機能が可能になります。家庭用電化製品、通信、自動車、製造、ヘルスケアなどの業界にサービスを提供し、コンパクトな設計、パフォーマンスの向上、効率的なシステム統合をサポートします。

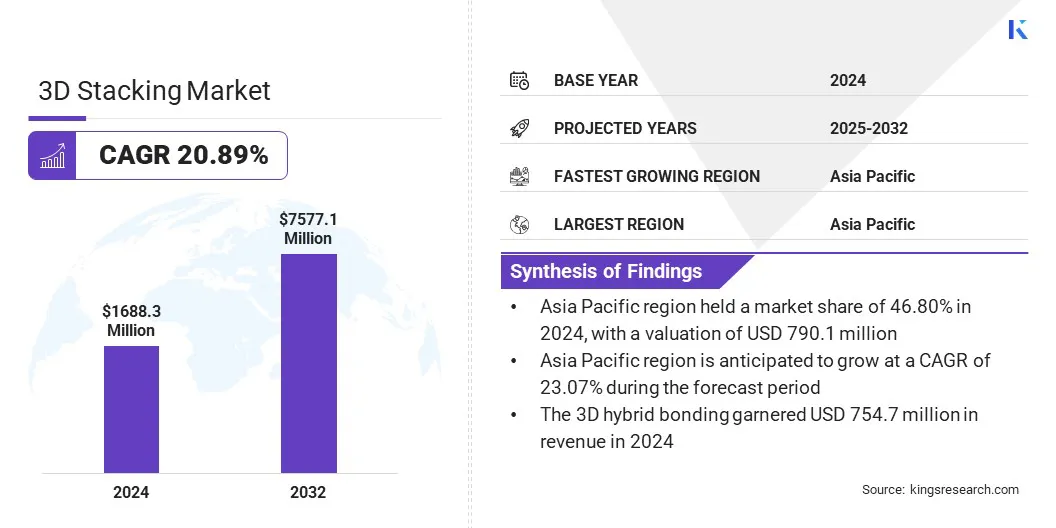

世界の 3D スタッキング市場規模は、2024 年に 16 億 8,830 万米ドルと評価され、2025 年の 20 億 830 万米ドルから 2032 年までに 75 億 7,710 万米ドルに成長すると予測されており、予測期間中に 20.89% の CAGR を示しています。

この成長は、高性能でエネルギー効率の高い半導体ソリューションを必要とする次世代カスタム アクセラレータの需要の増加によって推進されています。異種集積のために極薄トランジスタ層をさまざまなウェーハ上に移動するなど、層転写技術の進歩により、相互接続密度とデバイスの性能が向上しています。

3D スタッキング市場で活動している主要企業は、Taiwan Semiconductor Manufacturing Company Limited、Intel Corporation、Samsung、Advanced Micro Devices, Inc.、SK HYNIX INC.、ASE、Amkor Technology、Powertech Technology Inc.、Jiangsu Changdian Technology Co., Ltd.、XMC、Tezzaron、BroadPak Corporation、X-FAB Silicon Foundries SE、United Microelectronics Corporation、および Texas Instruments Incorporated です。

市場の成長は、AI アクセラレータ向けの高度なマルチダイ パッケージングの採用によって推進されており、これにより単一パッケージ内に複数の高性能チップを統合できます。これにより、AI と機械学習のワークロードの処理速度が向上し、レイテンシが短縮され、エネルギー効率が向上します。

メーカーは革新的な相互接続と熱管理ソリューションを活用して、高密度実装アーキテクチャのパフォーマンスと信頼性を最適化しています。このテクノロジーはスケーラブルで柔軟な設計をサポートし、企業が次世代 AI アプリケーションの増大する計算需要に対応できるようにします。

次世代カスタム アクセラレータに対する需要の高まり

3D スタッキング市場は、次世代のカスタム アクセラレータに対する需要の高まりによって牽引されています。ハイパフォーマンスコンピューティング、人工知能、データセンターアプリケーション。 3D スタッキングは、複数の半導体層を 1 つのパッケージ内に統合することで高速処理とエネルギー効率を可能にし、最新のアクセラレータの性能ニーズを満たします。

これにより、メーカーはコンパクトな設置面積を維持しながら、より高い計算能力と待ち時間の短縮を実現できます。特殊なコンピューティング アプリケーションのパフォーマンス向上に対する需要により、さまざまな業界で 3D スタッキング テクノロジの導入が加速しています。

3D スタッキング デバイスの熱管理の問題

3D スタッキング市場の主要な課題は、高密度にスタックされたチップの熱放散を管理することです。層密度が増加すると、より多くの熱が発生し、デバイスのパフォーマンスと信頼性が低下する可能性があります。これにより、特に高性能コンピューティングや小型電子機器における広範な採用が制限されます。

これに対処するために、企業はマイクロ流体冷却や改良された熱拡散材料などの高度な熱管理ソリューションに投資しています。メーカーはまた、放熱を強化し、一貫したパフォーマンスを維持するために、チップ アーキテクチャと積層設計を最適化しています。

レイヤー転送テクノロジーの進歩

3D スタッキング市場の主要なトレンドは、異種統合の進歩により可能になった、多様なウェーハ上への極薄トランジスタ層転写の使用です。これにより、メーカーはさまざまな半導体層を効率的に積層できるようになり、相互接続密度と信号の整合性が向上します。

また、単一パッケージ内でロジック、メモリ、特殊チップを組み合わせることも可能になり、デバイス全体のパフォーマンスが向上します。企業は、小型、高性能、エネルギー効率の高い電子機器に対する需要の高まりに応えるために、この技術を採用しています。

|

セグメンテーション |

詳細 |

|

方法別 |

チップ対チップ、チップ対ウェーハ、ダイ対ダイ、ダイ対ウェーハ、ウェーハ対ウェーハ |

|

相互接続技術による |

3D ハイブリッド ボンディング、3D TSV (シリコン貫通ビア)、モノリシック 3D 統合 |

|

デバイスの種類別 |

メモリデバイス、ロジックIC、イメージングおよびオプトエレクトロニクス、LED、MEMS/センサー、その他 |

|

最終用途産業別 |

家庭用電化製品、通信、自動車、製造、医療機器およびヘルスケア、その他 |

|

地域別 |

北米:アメリカ、カナダ、メキシコ |

|

ヨーロッパ: フランス、イギリス、スペイン、ドイツ、イタリア、ロシア、その他のヨーロッパ | |

|

アジア太平洋地域: 中国、日本、インド、オーストラリア、ASEAN、韓国、その他のアジア太平洋地域 | |

|

中東とアフリカ: トルコ、アラブ首長国連邦、サウジアラビア、南アフリカ、その他の中東およびアフリカ | |

|

南アメリカ: ブラジル、アルゼンチン、その他の南米 |

地域に基づいて、市場は北米、ヨーロッパ、アジア太平洋、中東およびアフリカ、南米に分類されています。

アジア太平洋地域の 3D スタッキング市場シェアは、2024 年に世界市場で 46.80% となり、評価額は 7 億 9,010 万ドルに達しました。この優位性は、大規模な半導体製造拠点の存在と、高度なパッケージング中国、日本、韓国などの国々の技術。

この地域の半導体企業は、コスト効率の高い生産、熟練した労働力、半導体インフラに対する政府の支援の恩恵を受けており、3D スタッキング ソリューションの幅広い採用を推進しています。

北米は、予測期間中に 19.68% の CAGR で成長する見込みです。この成長は、革新的な素材と高度な 3D スタッキング技術に重点を置いた強力な研究開発努力によって推進されています。この地域の半導体企業は研究施設と戦略的パートナーシップを活用してチップの効率と密度を向上させ、家電、自動車、通信分野での採用を加速させています。

世界の 3D スタッキング業界の主要企業は、高度な材料イノベーションを通じてデバイスのパフォーマンスと効率を向上させることに注力しています。企業は、チップの静電容量を低減する新材料を開発する研究に投資しており、これにより、スタックされたロジックおよび DRAM チップの信号整合性が向上し、消費電力が削減されます。

メーカーは、高密度 3D 構造のパフォーマンスの安定性を維持するために、複雑な熱管理ソリューションを実装しています。さらに、市場関係者は、これらの材料の採用を加速し、高性能アプリケーション向けの 3D 積層プロセスを最適化するために、機器サプライヤーや研究機関との戦略的コラボレーションを追求しています。

よくある質問