市场定义

3D堆叠过程将多个半导体层集成到单个软件包中,以增强设备性能并降低足迹。它结合了先进的互连技术,例如3D混合键,通过硅质VIA和单片3D整合,以实现更高的速度,效率和密度。

此过程应用于内存,逻辑IC,成像组件,LED和MEMS传感器等设备,从而启用各种功能。它为消费电子,通信,汽车,制造业和医疗保健等行业提供服务,支持紧凑的设计,提高性能和有效的系统集成。

3D堆叠市场概述

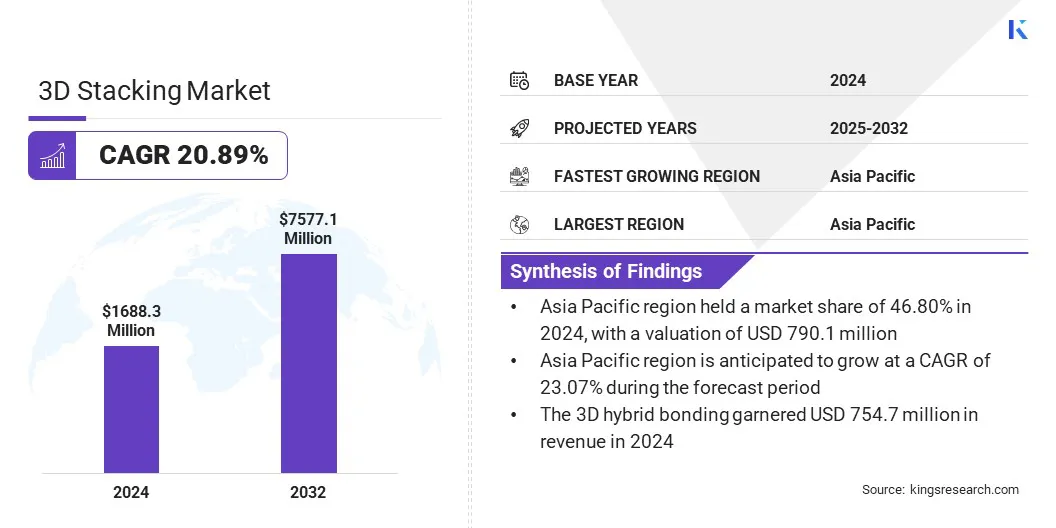

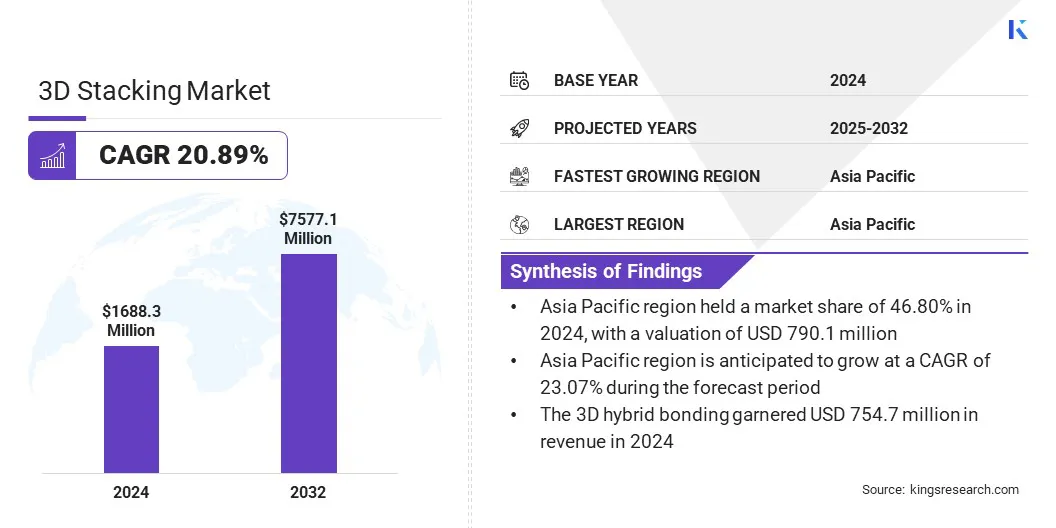

全球3D堆叠市场规模在2024年的价值为16.883亿美元,预计在2032年的2025年将从2025年的2,00830万美元增长到75.771亿美元,在预测期内的复合年增长率为20.89%。

增长是由对下一代定制加速器的需求不断增长的,这需要高性能和节能的半导体解决方案。层转移技术的进步,例如将超薄晶体管层转移到不同的晶状体上以进行异质整合,正在改善互连密度和设备性能。

关键亮点:

- 2024年,3D堆叠行业规模的记录为16.883亿美元。

- 从2025年到2032年,市场预计将以20.89%的复合年增长率增长。

- 亚太在2024年的市场份额为46.80%,估值为7.901亿美元。

- Chip-to-Chip部门在2024年获得了4.997亿美元的收入。

- 到2032年,3D混合粘合部门预计将达到43.612亿美元。

- 到2032年,内存设备细分市场预计将达到27.753亿美元。

- 预计到2032年,消费电子产品预计将达到2,0.518亿美元。

- 预计北美将在预测期内以19.68%的复合年增长率增长。

在3D堆叠市场开展业务的主要公司是台湾半导体制造公司有限公司,英特尔公司,三星,高级Micro Decessices,Inc。,SK Hynix Inc.,ASE,AMKOR Technologry,Powertech Technology Inc.,Powertech Technology Inc.,Jiangsu Changdian Technology Co.公司和德州仪器公司。

通过为AI加速器采用先进的多-DIE包装来推动市场的增长,这使得可以在一个包装中集成多个高性能芯片。这可以提高处理速度,降低延迟并提高AI和机器学习工作负载的能源效率。

制造商正在利用创新的互连和热管理解决方案来优化密集的架构的性能和可靠性。该技术支持可扩展和灵活的设计,使公司能够满足下一代AI应用程序的计算需求不断增长。

- 2025年5月,Marvell Technology,Inc。启动了一个专为定制AI加速器设计的新的多DIE包装平台。该平台允许更大的多芯片配置,同时降低功耗和整体成本,并提高模具与DIE互连效率。它结合了模块化的RDL插入器作为常规硅插入器的替代方案,并支持HBM3/3E内存集成。

市场驱动力

对下一代定制加速器的需求不断增长

3D堆叠市场是由对下一代定制加速器的需求不断增长的,这对于高性能计算,人工智能和数据中心应用程序。 3D堆叠通过将多个半导体层集成到单个软件包中,满足现代加速器的性能需求,从而实现高速处理和能源效率。

这使制造商可以在保持紧凑的足迹的同时获得更高的计算能力和减少潜伏期。在专业计算应用程序中,对增强性能的需求正在加速在各个行业中采用3D堆叠技术。

- 2024年12月,Broadcom Inc.在软件包(XDSIP)平台中引入了其3.5D极限系统,以支持自定义AI XPU。该平台将3D硅与2.5D包装合并,从而可以在一个包装中集成多个计算模具,I/O模具和HBM内存堆栈。它可以提高互连密度,降低功耗并降低延迟,同时维持AI应用程序的紧凑套件设计。

市场挑战

3D堆叠设备中的热管理问题

3D堆叠市场的一个主要挑战是管理高密度堆叠芯片的散热。增加的层密度会产生更多的热量,从而降低设备性能和可靠性。这限制了广泛的采用,尤其是在高性能计算和紧凑的电子设备中。

为了解决这个问题,公司正在投资先进的热管理解决方案,包括微流体冷却和改进的热量材料。制造商还正在优化芯片建筑和堆叠设计,以增强散热量并保持一致的性能。

市场趋势

层转移技术的进步

3D堆叠市场的一个关键趋势是将超薄晶体管层转移到多种晶圆上,这是由于异质整合的进步而实现的。这使制造商可以有效地堆叠多样化的半导体层,从而提高互连密度和信号完整性。

它还可以在单个软件包中结合逻辑,内存和专业芯片,从而增强整体设备性能。公司正在采用这项技术来满足对紧凑,高性能和节能电子设备的不断增长的需求。

- 2025年6月,Soitec和PowerChip半导体制造公司(PSMC)宣布了一项战略合作,以推动NM级3D堆叠的超薄晶体管层转移(TLT)技术。该合作伙伴关系致力于为300mm的基板提供释放层,以实现超薄晶体管层的高速传输,并支持下一代3D芯片堆叠。

3D堆叠市场报告快照

|

分割

|

细节

|

|

通过方法

|

芯片到芯片,芯片到纸片,死与饮食,死去的晶圆,晶圆到蜡笔

|

|

通过互连技术

|

3D混合键合,3D TSV(通过silicon via),单片3D整合

|

|

按设备类型

|

内存设备,逻辑IC,成像和光电学,LED,MEM/传感器,其他

|

|

通过最终用途行业

|

消费电子,通信,汽车,制造,医疗设备和医疗保健,其他

|

|

按地区

|

北美:美国,加拿大,墨西哥

|

|

欧洲:法国,英国,西班牙,德国,意大利,俄罗斯,欧洲其他地区

|

|

亚太:中国,日本,印度,澳大利亚,东盟,韩国,亚太其他地区

|

|

中东和非洲:土耳其,阿联酋,沙特阿拉伯,南非,中东和非洲的其他地区

|

|

南美洲:巴西,阿根廷,南美其他地区

|

市场细分:

- 通过方法(芯片到芯片,芯片到芯片,死去,死去,胜利和晶圆碎片):由于紧凑型和高性满的电子设备的高采用,2024年的芯片到芯片段在2024年获得了4.997亿美元。

- 通过互连技术(3D混合键合,3D TSV(通过silicon via)和Monolithic 3D整合):由于其较高的互连密度和改善的信号性能,3D混合键合段在2024年占市场的44.70%。

- 根据设备类型(内存设备,逻辑IC,成像和光电学,LED,MEM/传感器等):由于对高可靠性和能源效率存储解决方案的需求增加,预计到2032年,内存设备段预计将达到27.753亿美元。

- 通过最终用途行业(消费电子,通信,汽车,制造,医疗设备和医疗保健等):由于智能手机和可穿戴设备中高级半导体的整合,预计到2032年,消费电子部门预计到2032年将达到2,0.518亿美元。

3D堆叠市场区域分析

根据地区,该市场已分为北美,欧洲,亚太地区,中东和非洲以及南美。

在全球市场上,亚太3D堆叠市场份额在2024年为46.80%,估值为7.901亿美元。这种主导地位是由于存在大型半导体制造枢纽以及高采用高级包装中国,日本和韩国等国家的技术。

该地区的半导体公司受益于成本效益的生产,熟练的劳动力以及政府对半导体基础设施的支持,推动了更广泛的3D堆叠解决方案的采用。

北美准备在预测期内以19.68%的复合年增长率增长。这种增长是由强大的研发工作驱动的,重点是创新材料和先进的3D堆叠技术。该地区的半导体公司利用研究设施和战略合作伙伴关系来提高芯片效率和密度,加速消费电子,汽车和通信领域的采用。

- 2025年4月,麻省理工学院林肯实验室开发了一种专门的基准测试芯片,以测试3D集成微电子学的冷却溶液。该芯片产生了高功率,以模拟堆叠电路中的热量,并在应用冷却方法时衡量温度变化。该项目由DARPA根据Minitherms3D计划资助,支持HRL实验室为3D异质集成堆栈开发热管理系统。

监管框架

- 在美国,工业与安全局(BIS)通过控制先进的半导体制造设备的出口并将转移到外国实体来调节3D堆叠技术。

- 在欧洲,欧洲委员会通过《欧洲芯片法》规定,该法案制定了投资,制造和创新激励措施的规定,以确保安全且有弹性的半导体供应链。

- 在日本,经济,贸易和工业部通过支持研究计划,制定行业标准并为国内半导体制造商提供激励措施来调节3D奇普的开发。

竞争格局

全球3D堆叠行业的主要参与者致力于通过先进的物质创新来提高设备性能和效率。公司正在投资研究以开发减少芯片电容的新材料,从而提高信号完整性并降低堆叠逻辑和DRAM芯片的功耗。

制造商正在实施复杂的热管理解决方案,以维持高密度3D结构的性能稳定性。此外,市场参与者正在与设备供应商和研究机构进行战略合作,以加速采用这些材料并优化3D堆叠过程,以用于高性能应用程序。

- 2024年7月,Applied Materials,Inc。推出了新的材料工程解决方案,以将铜芯片接线扩展到2NM节点及以后。该溶液结合钌和钴,以将电阻降低25%,并引入增强的低K介电介质,从而增强逻辑和DRAM芯片,以用于高级3D堆叠。预计这将提供高能节能的计算和提高的芯片性能。

心脏标记测试市场中的主要公司:

- 台湾半导体制造公司有限公司

- 英特尔公司

- 三星

- Advanced Micro Devices,Inc。

- SK Hynix Inc。

- ASE

- Amkor技术

- PowerTech Technology Inc.

- 江苏宽大技术有限公司

- XMC

- Tezzaron

- Broadpak Corporation

- X-fab硅铸造厂SE

- 联合微电子公司

- Texas Instruments Incorporated

最近的发展(合作伙伴/新产品发布)

- 2025年8月,Socionext Inc.通过先进的3D解决方案扩展了其投资组合,包括增强的3D模具堆叠和5.5D包装技术。产品的面对面特征(F2F)3D Compute和N5 I/O DIES堆叠,可为消费者,AI和HPC应用程序提供更高的集成密度,较低的功耗以及提高性能。

- 2024年6月,ANSYS宣布与Nvidia Omniverse的集成,以启用3D多物理学可视化下一代3D-IC设计。该协作使设计师可以实时与电磁和热模型进行交互,从而改善了5G/6G,AI/ML,IoT和自动驾驶汽车在内的应用程序的诊断和优化。该解决方案支持多-DIE芯片堆栈,有助于优化紧凑型半导体软件包的性能,可靠性和功率效率。

重要的

常见问题

在预测期内,3D堆叠市场的预期复合年增长率是多少? 预计哪个细分市场将在2032年占有最大的市场份额?