市場の定義

3Dスタッキングプロセスは、複数の半導体層を単一のパッケージに統合して、デバイスの性能を高め、フットプリントを削減します。 3Dハイブリッド結合、スルーシリコンバイアス、モノリシック3D統合などの高速な相互接続技術を組み合わせて、高速、効率、密度を実現します。

このプロセスは、メモリ、ロジックIC、イメージングコンポーネント、LED、MEMSセンサーなどのデバイスに適用され、多様な機能を可能にします。家電、通信、自動車、製造、ヘルスケアなどの産業にサービスを提供し、コンパクトな設計、パフォーマンスの向上、効率的なシステム統合をサポートしています。

3Dスタッキング市場概要

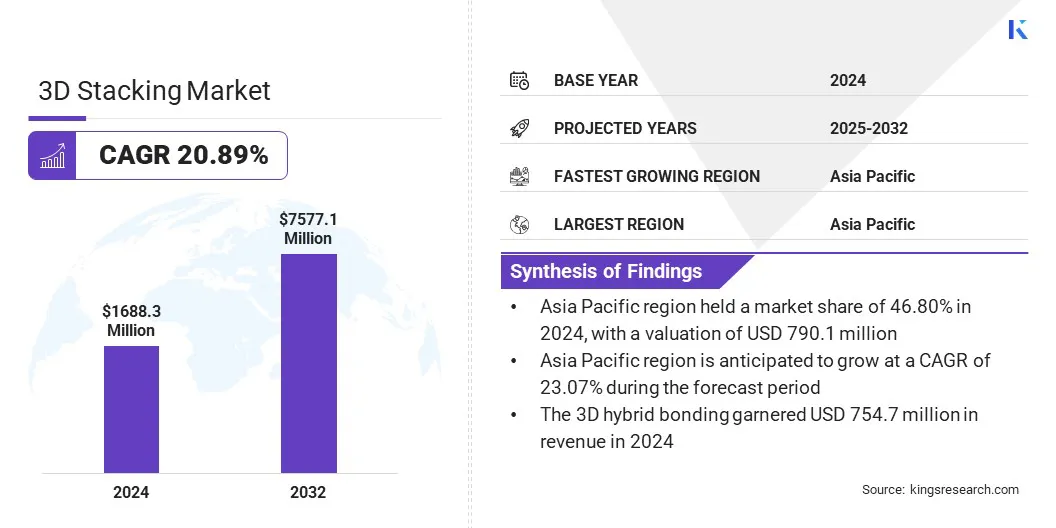

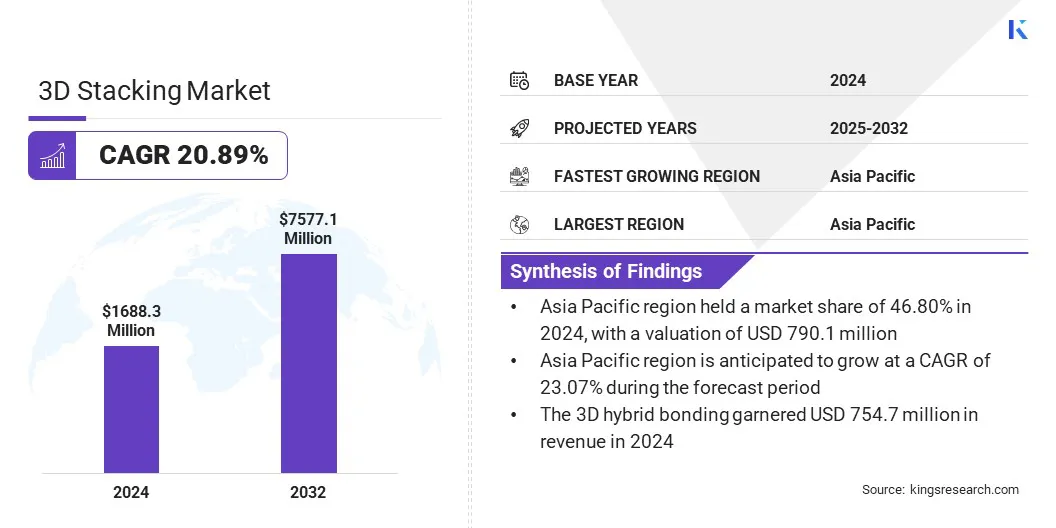

世界の3Dスタッキング市場規模は、2024年の1,688.3百万米ドルと評価され、2025年の2,008.3百万米ドルから2032年までに7,577.1百万米ドルに成長すると予測されており、予測期間にわたって20.89%のCAGRを示しました。

成長は、高性能およびエネルギー効率の高い半導体ソリューションを必要とする次世代カスタムアクセラレータに対する需要の増加によって促進されます。不均一な統合のために、超薄型トランジスタ層を多様なウェーハに移動するなど、層移動技術の進歩により、相互接続密度とデバイスのパフォーマンスが向上しています。

重要なハイライト:

- 3Dスタッキング業界規模は、2024年に1,688.3百万米ドルで記録されました。

- 市場は、2025年から2032年まで20.89%のCAGRで成長すると予測されています。

- アジア太平洋地域は、2024年に46.80%の市場シェアを保有し、7億9,010万米ドルの評価を受けています。

- チップからチップへのセグメントは、2024年に4億9,970万米ドルの収益を集めました。

- 3Dハイブリッドボンディングセグメントは、2032年までに4,361.2百万米ドルに達すると予想されます。

- メモリデバイスセグメントは、2032年までに2,7735万米ドルに達すると予想されます。

- コンシューマーエレクトロニクスセグメントは、2032年までに2,05180万米ドルに達すると予想されています。

- 北米は、予測期間中に19.68%のCAGRで成長すると予想されています。

3Dスタッキング市場で事業を展開している大手企業は、台湾半導体製造会社Limited、Intel Corporation、Samsung、Advanced Micro Devices、Inc.、SK Hynix Inc.、ASE、Amkor Technology、Powertech Technology Inc.、Jiangsu Changdian Technology Co.、Ltd。、Ltd。、Ltd.、Xmc、Tezzaron、X-fab Sileconson、X-Fab Sileconson、X-Fab Sileconon、テキサスインストゥルメントが組み込まれています。

市場の成長は、AIアクセラレータ向けの高度なマルチダイパッケージの採用によって推進され、単一のパッケージ内の複数の高性能チップの統合を可能にします。これにより、処理速度が向上し、レイテンシーが低下し、AIおよび機械学習ワークロードのエネルギー効率が向上します。

メーカーは、革新的な相互接続と熱管理ソリューションを活用して、密集したアーキテクチャのパフォーマンスと信頼性を最適化しています。このテクノロジーは、スケーラブルで柔軟な設計をサポートしており、企業は次世代AIアプリケーションの増加する計算需要を満たすことができます。

- 2025年5月、Marvell Technology、Inc。は、カスタムAIアクセラレータ向けに設計された新しいマルチダイパッケージングプラットフォームを立ち上げました。このプラットフォームにより、消費電力と全体的なコストを削減しながら、より大きなマルチチップ構成が可能になり、ダイとダイの相互接続効率が向上します。従来のシリコンインターポーザーの代替としてモジュラーRDLインターポーザーを組み込み、HBM3/3Eメモリ統合をサポートします。

マーケットドライバー

次世代のカスタムアクセラレータに対する需要の高まり

3Dスタッキング市場は、次世代のカスタムアクセラレータに対する需要の高まりによって推進されています。高性能コンピューティング、人工知能、およびデータセンターアプリケーション。 3Dスタッキングにより、単一のパッケージ内に複数の半導体層を統合して、最新の加速器のパフォーマンスニーズを満たすことにより、高速処理とエネルギー効率が可能になります。

これにより、メーカーはコンパクトなフットプリントを維持しながら、より高い計算能力とレイテンシを達成できます。専門的なコンピューティングアプリケーションでのパフォーマンスの向上の需要は、さまざまな業界で3Dスタッキングテクノロジーの採用を加速しています。

- 2024年12月、Broadcom Inc.は、カスタムAI XPUをサポートするために、パッケージ(XDSIP)プラットフォームに3.5D Extreme Dimension Systemを導入しました。このプラットフォームは、3Dシリコンスタッキングと2.5Dパッケージングをマージし、複数のコンピューティングダイ、I/Oダイ、およびHBMメモリスタックを単一のパッケージに統合します。相互接続密度を改善し、電力消費を低下させ、レイテンシを減らし、AIアプリケーションのコンパクトなパッケージ設計を維持します。

市場の課題

3Dスタッキングデバイスの熱管理の問題

3Dスタッキング市場での主要な課題は、高密度スタッキングチップの熱散逸を管理することです。層密度の増加により、より多くの熱が生成されるため、デバイスのパフォーマンスと信頼性が低下します。これにより、特に高性能コンピューティングとコンパクトな電子デバイスでは、広範な採用が制限されます。

これに対処するために、企業はマイクロ流体冷却や改善された熱を吸収する材料など、高度な熱管理ソリューションに投資しています。メーカーは、熱散逸を強化し、一貫したパフォーマンスを維持するために、チップアーキテクチャとスタッキングデザインを最適化しています。

市場動向

層移転技術の進歩

3Dスタッキング市場の重要な傾向は、異種の統合の進歩によって有効になっている多様なウェーハへの超薄型トランジスタ層の転送を使用することです。これにより、メーカーは多様な半導体層を効率的に積み重ね、相互接続密度と信号の完全性を改善することができます。

また、単一のパッケージ内のロジック、メモリ、および特殊なチップの組み合わせを可能にし、デバイス全体のパフォーマンスを向上させます。企業は、コンパクト、高性能、およびエネルギー効率の高い電子デバイスに対する需要の高まりを満たすために、この手法を採用しています。

- 2025年6月、SoitecおよびPowerChip Semiconductor Manufacturing Corporation(PSMC)は、NMスケール3Dスタッキング用の超薄型トランジスタ層移転(TLT)テクノロジーを前進させるための戦略的コラボレーションを発表しました。このパートナーシップは、300mm基板にリリース層を供給することに焦点を当てており、超薄型トランジスタ層の高速移動を可能にし、次世代の3Dチップスタッキングをサポートします。

3Dスタッキング市場レポートスナップショット

|

セグメンテーション

|

詳細

|

|

メソッドによって

|

チップからチップ、チップからワーファー、ダイ、ダイ、ダイオーファー、ウェーハツーウェーファー

|

|

テクノロジーを相互接続することにより

|

3Dハイブリッドボンディング、3D TSV(スルーシリコンVIA)、モノリシック3D統合

|

|

デバイスタイプごとに

|

メモリデバイス、論理ICS、イメージングおよびオプトエレクトロニクス、LED、MEMS/センサー、その他

|

|

最終用途業界による

|

家電、通信、自動車、製造、医療機器、ヘルスケア、その他

|

|

地域別

|

北米:米国、カナダ、メキシコ

|

|

ヨーロッパ:フランス、英国、スペイン、ドイツ、イタリア、ロシア、ヨーロッパのその他

|

|

アジア太平洋:中国、日本、インド、オーストラリア、ASEAN、韓国、アジア太平洋地域の残り

|

|

中東とアフリカ:トルコ、U.A.E。、サウジアラビア、南アフリカ、中東の残りの部分とアフリカ

|

|

南アメリカ:ブラジル、アルゼンチン、南アメリカの残り

|

市場セグメンテーション:

- メソッド(チップからチップ、チップ、チップからワーファー、ダイ、ダイ、ダイオーファー、ウェーハツーワーファー):チップからチップへのセグメントは、コンパクトおよび高性能の電子デバイスの高い採用により、2024年に499.7百万米ドルを獲得しました。

- 相互接続テクノロジー(3Dハイブリッドボンディング、3D TSV(スルーシリコンVIA)、およびモノリシック3D統合):3Dハイブリッドボンディングセグメントは、2024年に市場の44.70%を保持しました。

- デバイスの種類(メモリデバイス、ロジックIC、イメージングとオプトエレクトロニクス、LED、MEMS/センサーなど):メモリデバイスセグメントは、2032年までに2,773300万米ドルに達すると予測されています。

- 最終用途の産業(家電、通信、自動車、製造、医療機器、医療など)によって:家電セグメントは、スマートフォンやウェアラブルの高度な半導体の統合が増加するため、2032年までに2,051.8百万米ドルに達すると予測されています。

3Dスタッキング市場地域分析

地域に基づいて、市場は北米、ヨーロッパ、アジア太平洋、中東、アフリカ、南アメリカに分類されています。

アジア太平洋地域の3Dスタッキング市場シェアは、2024年に世界市場で46.80%であり、790.1百万米ドルの評価がありました。この優位性は、大規模な半導体製造ハブの存在と高い採用によるものです高度なパッケージ中国、日本、韓国などの国の技術。

この地域の半導体企業は、費用効率の高い生産、熟練した労働力、および半導体インフラストラクチャに対する政府の支援の恩恵を受け、3Dスタッキングソリューションの幅広い採用を推進しています。

北米は、予測期間中に19.68%のCAGRで成長する態勢を整えています。この成長は、革新的な材料と高度な3Dスタッキング技術に焦点を当てた強力なR&Dの取り組みによって推進されています。この地域の半導体企業は、研究施設と戦略的パートナーシップを利用して、チップの効率と密度を改善し、家電、自動車、および通信セクターの採用を加速させます。

- 2025年4月、MITリンカーン研究所は、3D統合マイクロエレクトロニクスの冷却ソリューションをテストするための専門のベンチマークチップを開発しました。チップは、積み重ねられた回路の熱をシミュレートするために高出力を生成し、冷却方法が適用されると温度変化を測定します。 Minitherms3Dプログラムの下でDARPAから資金提供を受けたこのプロジェクトは、3D不均一な統合スタック向けの熱管理システムの開発におけるHRL研究所をサポートしています。

規制枠組み

- 米国で、産業セキュリティ局(BIS)は、高度な半導体製造装置の輸出を制御し、外国企業への転送を制限することにより、3Dスタッキング技術を規制しています。

- ヨーロッパで、欧州委員会は、投資、製造、イノベーションのインセンティブに関する規則を設定し、安全で回復力のある半導体サプライチェーンを確保する欧州チップス法を通じて規制しています。

- 日本で、経済貿易産業省は、研究プログラムをサポートし、業界の基準を設定し、国内の半導体メーカーにインセンティブを提供することにより、3Dチップレット開発を規制しています。

競争力のある風景

グローバル3Dスタッキング業界の主要なプレーヤーは、高度な材料革新を通じてデバイスのパフォーマンスと効率を向上させることに焦点を当てています。企業は、チップ容量を減らす新しい材料を開発するために研究に投資しています。これにより、信号の完全性が向上し、積み重ねられたロジックとDRAMチップの消費電力が低下します。

メーカーは、高密度3D構造の性能の安定性を維持するために、複雑な熱管理ソリューションを実装しています。さらに、マーケットプレーヤーは、これらの材料の採用を加速し、高性能アプリケーションの3Dスタッキングプロセスを最適化するために、機器サプライヤーおよび研究機関との戦略的コラボレーションを追求しています。

- 2024年7月、Applied Materials、Inc。は、銅チップの配線を2nmノード以降に拡張するための新しい材料エンジニアリングソリューションを発売しました。この溶液は、ルテニウムとコバルトを組み合わせて最大25%電気抵抗を減らし、高度な3Dスタッキングのためにロジックを強化し、DRAMチップを強化する強化された低k誘電体を導入します。これは、非常にエネルギー効率の高いコンピューティングとCHIPパフォーマンスの向上を提供すると予想されています。

心臓マーカーテスト市場の主要企業:

- 台湾半導体製造会社Limited

- Intel Corporation

- サムスン

- Advanced Micro Devices、Inc。

- Sk Hynix Inc。

- ase

- Amkorテクノロジー

- Powertech Technology Inc.

- Jiangsu Changdian Technology Co.、Ltd。

- XMC

- テッツァロン

- Broadpak Corporation

- X-fabシリコンファウンドリースSE

- United Microelectronics Corporation

- テキサスインストゥルメントが組み込まれています

最近の開発(パートナーシップ/新製品の発売)

- 2025年8月、Socionext Inc.は、強化された3Dダイスタッキングや5.5Dパッケージングテクノロジーなど、高度な3DICソリューションでポートフォリオを拡張しました。このオファリングは、N3コンピューティングとN5 I/Oダイの対面(F2F)3Dスタッキングを特徴としており、消費者、AI、およびHPCアプリケーションの統合密度、低い消費電力、パフォーマンスの向上を可能にします。

- 2024年6月、ANSYSは、Nvidia Omniverseとの統合を発表し、次世代3D-ICデザインの3D多目的視覚化を可能にしました。このコラボレーションにより、設計者は電磁モデルと熱モデルとリアルタイムでやり取りできるようになり、5G/6G、AI/ML、IoT、および自律車両を含むアプリケーションの診断と最適化が改善されます。このソリューションは、マルチダイチップスタックをサポートし、コンパクトな半導体パッケージのパフォーマンス、信頼性、電力効率を最適化するのに役立ちます。

重要な

よくある質問

予測期間にわたって3Dスタッキング市場に期待されるCAGRは何ですか? どの地域が予測期間にわたって市場で最も急速に成長すると予想されていますか? 2032年に市場で最大のシェアを保有すると予想されるセグメントはどれですか?